# EDEC Chip Design Contest \*

Design of a 15.4–17 GHz Current-Reused Coupled VCO and Improved Noise Circulation with Enhanced Flicker Noise Suppression at 1/f<sup>3</sup>

Corner

Aulya Sholehah Wataawa Sau, Muhammad Fakhri Mauludin, Student Member, IEEE, and Jusung Kim, Member, IEEE

#### Introduction

VCOs are vital for frequency synthesizers and PLLs, with performance impacting phase noise (PN), tuning range, supply pushing, start-up, and power consumption. These parameters are interdependent, making optimization difficult, especially at millimeter-wave frequencies. A key trade-off exists between low PN and wide tuning range, limiting performance at higher frequencies.

# **Proposed Circuit Design**

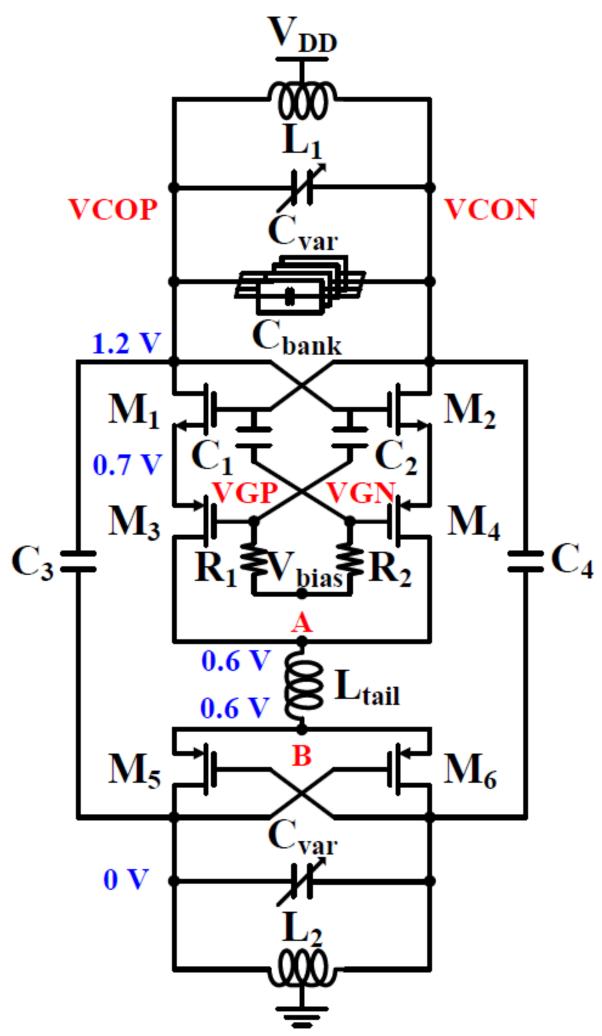

The proposed VCO uses a current-reused coupled oscillator with triode-biased degeneration to enhance ISF symmetry and suppress flicker noise. Capacitive coupling replaces bulky transformers, and a tail inductor filters second harmonics while maintaining high tank Q.

Fig 1. Schematic of the proposed VCO

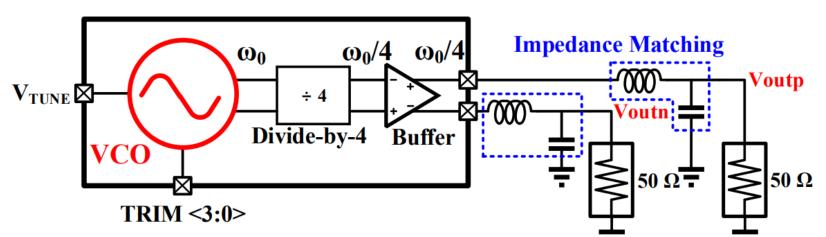

The implemented prototype circuits, where the output of VCO is post-processed by divide-by-4 and output buffer.

**Fig 2.** Block diagram of the prototype circuits consisting of the proposed VCO, divide-by-4, and output-buffer.

## Fabrication & Measurement Result

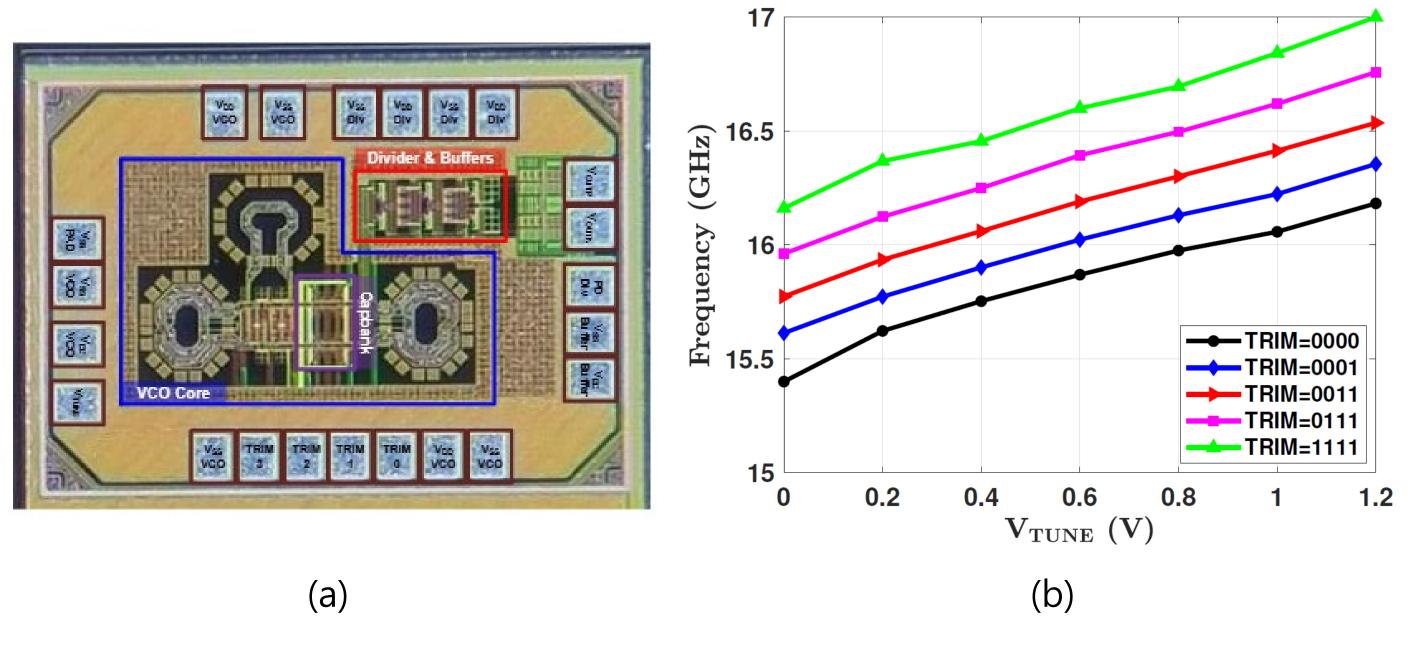

• The prototype circuit was fabricated in a 65nm CMOS technology. The entire chip occupies 590  $\times$  850  $\mu m^2$ . The VCO consumes 6.72 - 5.9 mW with tuning range from 15.4–17 GHz.

**Fig 3.** (a) Chip micrograph of the proposed VCO (b) Measurement results of frequency tuning range.

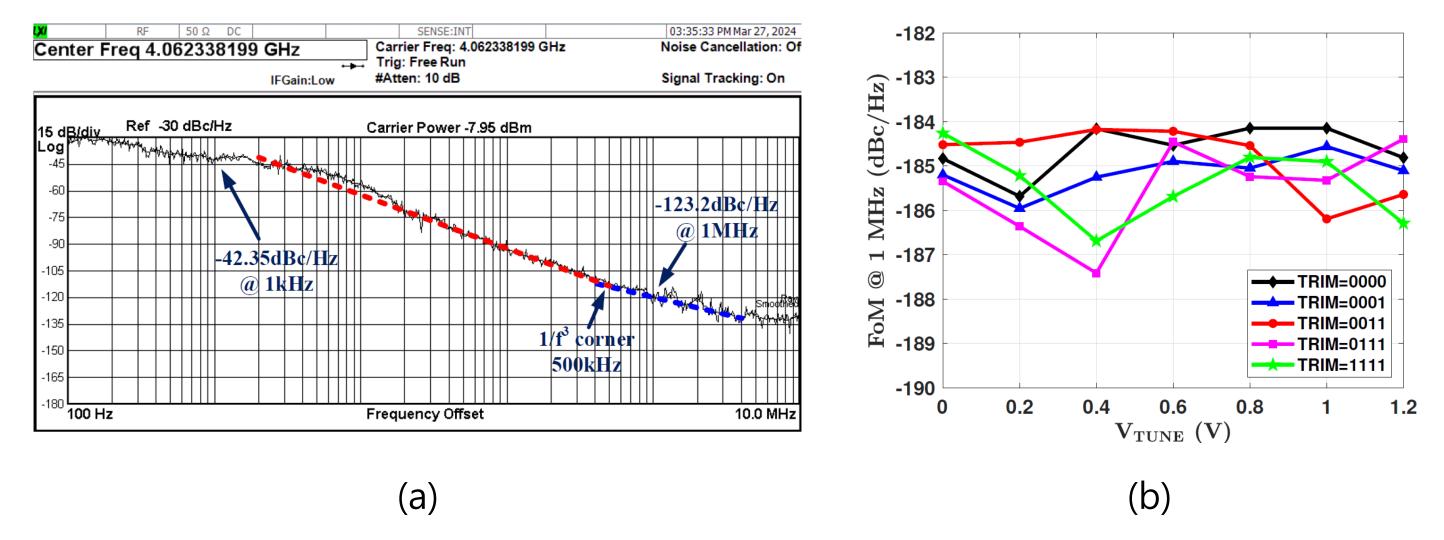

• The measured best phase noise reached at -123.3 dBc/Hz at 1MHz frequency offset with 500 kHz 1/f³ corner at 4.06 GHz output frequency.

**Fig 4. (a)** Measured PN after divide-by-4 of the prototype circuit at best PN frequency (b) FoM of the proposed circuit over different capacitor bank trims and control voltages at 1 MHz offset.

## Conclusion

A VCO design achieving low phase noise, low power, and high  $K_{VCO}$  VCO is presented. Measured at 16.25 GHz, phase noise is -30.3 dBc/Hz at 1 kHz and -111.2 dBc/Hz at 1 MHz offsets shows the best performances at the proposed VCO. The improved noise circulation technique reduces close-in noise while preserving  $1/f^2$  performance.